Revolutionizing

Computing

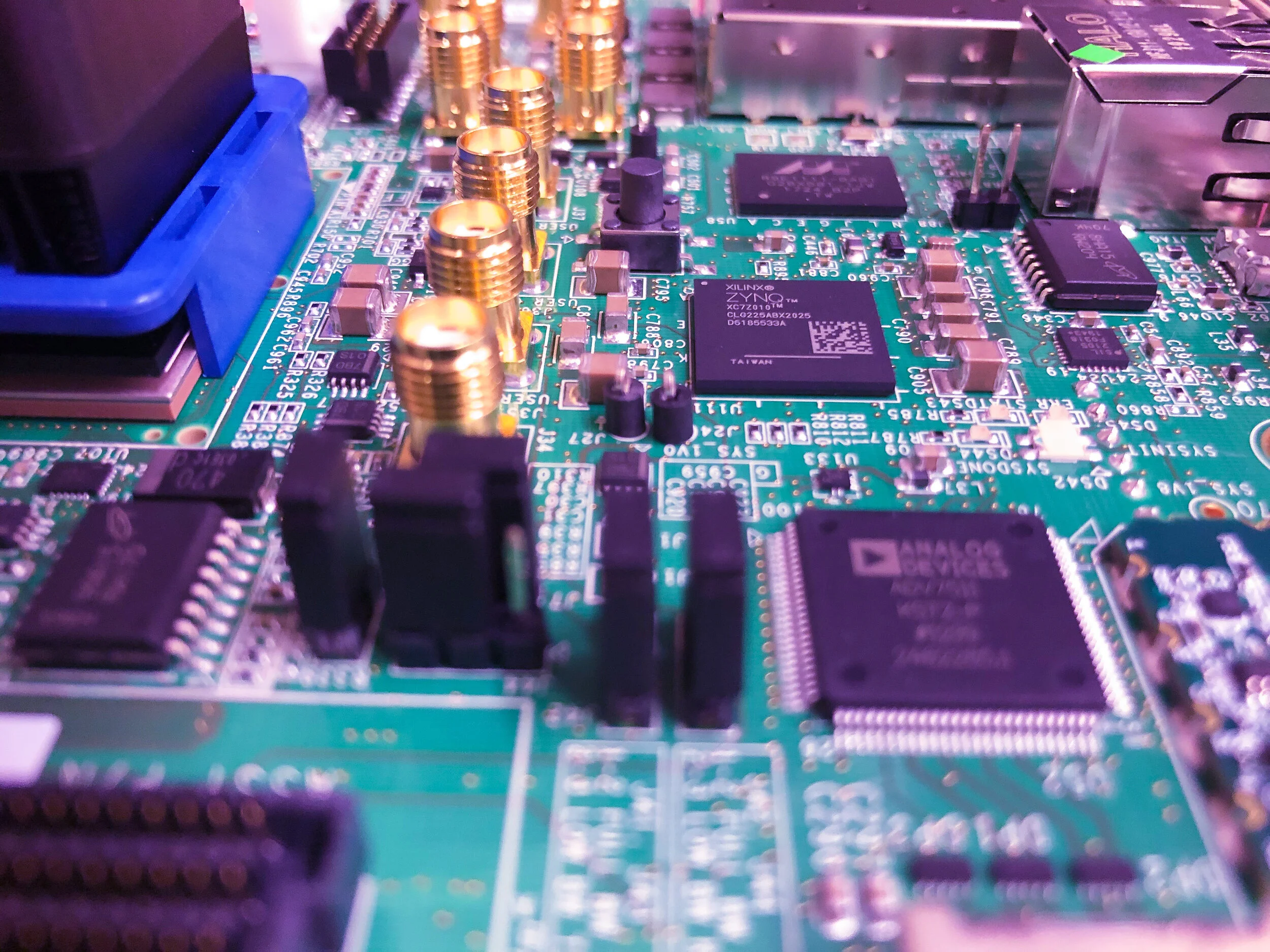

Unary computing is a new, unconventional paradigm in digital computing in which an “uncompressed” data representation (unary) is used instead of the traditional binary representation to make computations very efficient. As validated by our experiments, using unary computing increases throughput (how fast computations are done), reduces hardware area (size and cost of the chips to perform computations), and reduces power (indirectly affects power consumption costs, and cooling costs). These are important metrics that have direct impacts on industry costs.

The proposed method is compatible with existing design methodologies and tools: all the measured costs include conversion from binary to unary, cost of computations, and cost of converting unary results back to binary. As a result, designers can integrate our computation methodology in existing digital designs because they can treat our computational units as black boxes that take binary inputs, and deliver binary outputs.

We have solutions for FPGAs in 5G applications, machine learning, video streaming, and high-frequency trading. We can provide FPGA IP cores, and also work with partners in developing integrated solutions.

Our Outstanding Team

Kia Bazargan

kia bazargan

Kia received the B.Sc. degree in computer science from Sharif University, Tehran, Iran, and the M.S. and Ph.D. degrees in electrical and computer engineering from Northwestern University, Evanston, IL, USA, in 1998 and 2000, respectively. He is currently an Associate Professor with the Department of Electrical and Computer Engineering, University of Minnesota. He was a recipient of the U.S. National Science Foundation Career Award. He was the Technical Program chair (2018), General Chair (2019) and finance chair (2020) of the Field Programmable Gate Array (FPGA) conference, the top conference in the field. Kia's research interests are FPGAs, CAD, Stochastic and Unary Computing. He holds 16 issued and pending patents on stochastic and unary computing, and is one of the world leaders in the field.

x

x bio.